## SILICON PERMEABLE BASE TRANSISTORS FOR LOW-PHASE-NOISE OSCILLATOR APPLICATIONS UP TO 20 GHz

Dennis D. Rathman\* and Walter K. Niblack\*\*

\* Lincoln Laboratory, Massachusetts Institute of Technology

Lexington, MA. 02173\*\* Loral Frequency Sources

Chelmsford, MA. 01824

## ABSTRACT

Silicon permeable base transistors have been fabricated that exhibit a small-signal short-circuit current gain frequency exceeding 20 GHz and a maximum frequency of oscillation near 30 GHz. This transistor has been used to realize voltage-controlled oscillators at C, X, and Ku band that have provided low phase noise.

## INTRODUCTION

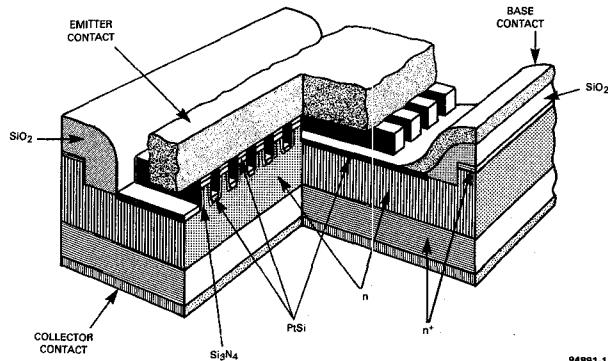

There has been considerable interest in developing novel transistor structures and geometries which provide high frequency performance. One such device is the permeable base transistor (PBT).<sup>1-3</sup> The important feature of the PBT is a thin Schottky-barrier base which is patterned into a submicrometer-periodicity grating. As shown in Figure 1, the active region of the Si PBT is formed from an array of 320-nm-period grooves etched in an n-type Si region. The Schottky-barrier base grid consists of a thin Pt-Si film in the groove bottoms. Although the Si device differs in structural detail from the GaAs version<sup>2</sup> in which the Schottky barrier base grid is entirely encapsulated by GaAs, the principle of operation remains the same. The electron current flows vertically through the openings between the grid-like base fingers. The device can be viewed essentially as a vertical FET, with a very short gate length, which accounts for its high frequency capability.

## FABRICATION DETAILS

The starting material for the device is a relatively high resistivity ( $3 \Omega \text{ cm}$ ) epitaxial n-layer grown on an n<sup>+</sup> substrate. The n-type layer is modified by two implants. One is a shallow As implant required for the ohmic contact on the top of the etched ridges. The other is a high energy (300-400 keV) P implant which provides a peak in the carrier concentration in the vicinity of the base grating adjacent to the bottoms of the etched grooves. This results in an active region doping profile that is  $10^{16} \text{ cm}^{-3}$  or higher in the emitter and base regions and approximately one order of magnitude lower in the collector region. Both our experimental measurements and numerical simulations indicate that this type of doping profile maintains the high f<sub>T</sub> of the device even for collector-to-base voltages of 15 V.

Fig. 1 Three-dimensional cross section of the silicon permeable base transistor.

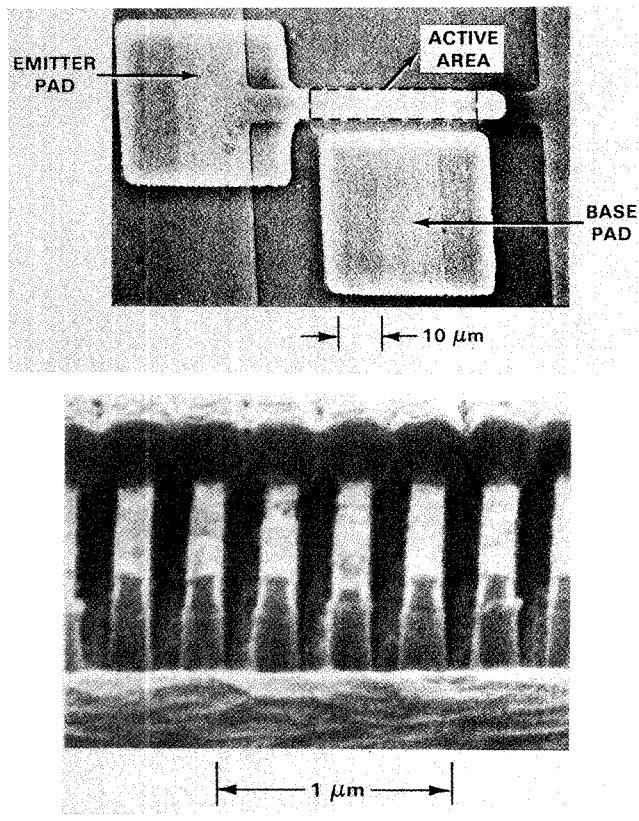

The critical step of the fabrication sequence is the formation of the straight-walled etched grooves of submicrometer-periodicity constituting the active region. This is accomplished using x-ray lithography and reactive ion etching, as previously described.<sup>3</sup> After the grating is formed, Si<sub>3</sub>N<sub>4</sub> is conformally deposited on the grating area using chemical vapor deposition. Anisotropic reactive ion etching is then used to remove this layer from the top of the ridges and the bottom of the grooves. A Pt film is then electron-beam evaporated and heat treated, resulting in the formation of a PtSi base. The Pt deposited on the Si<sub>3</sub>N<sub>4</sub>-coated sidewalls does not react with the Si and can be etched away. The Si<sub>3</sub>N<sub>4</sub> layer therefore serves the dual role of passivating the sidewalls and of facilitating the Pt removal from the grating sidewalls. The PtSi on top of the ridges is then connected together by a sequence of W and Al angle evaporation which form an Al-W bridge. The etched-groove Si grating, the Al-W bridge, and the base and emitter contact pads are shown in the scanning electron micrograph (SEM) sequence of Figure 2. For the devices shown, the grating periodicity is 320 nm, the etched-groove depth is ~500 nm, the PtSi thickness is 60 nm, and the device active region is 40  $\mu\text{m} \times 8 \mu\text{m}$ .

## SMALL-SIGNAL MEASUREMENTS

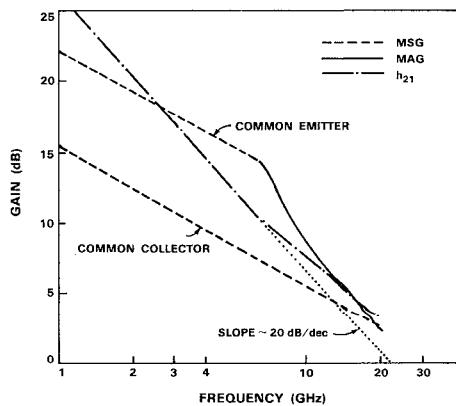

Figure 3 shows scattering-parameter measurements from 1-20 GHz which were performed with the transistor chips mounted on ceramic carriers. The devices were bonded in either common-emitter or common-collector configuration. Although the top contact can function as either

Fig. 2 SEM micrograph of a completed Si PBT. The upper half of the figure shows the bonding pads and the active region of the device. The bottom half of the figure is a close up of the 320-nm-period grating and the Al-W bridge.

Fig. 3 Maximum stable gain, maximum available gain, and short-circuit current gain as a function of frequency for the Si PBT measured with the top contact as the emitter.

the emitter or collector of the device (see Figure 1), all data reported in this paper were taken with the top contact operating as the emitter. The short-circuit current gain ( $h_{21}$ ) extrapolates at a 20 dB/decade roll-off and reaches unity at a frequency  $f_T$  of 22 GHz. Maximum values of  $f_T$  between 17 GHz and 22 GHz were typical of the devices measured. When measured in a common-emitter configuration, the maximum available gain was approximately 9 dB at 10 GHz, which extrapolates to a maximum frequency of oscillation ( $f_{max}$ ) near 30 GHz. In the common-collector configuration the necessary bias conditions increase the ratio of the base-to-emitter capacitance to the base-to-collector capacitance. Because of this the PBT has lower gain and stability, and only maximum stable gain can be measured to 20 GHz. As a result, the Si PBT is particularly well-suited for use as an oscillator in the common-collector configuration.

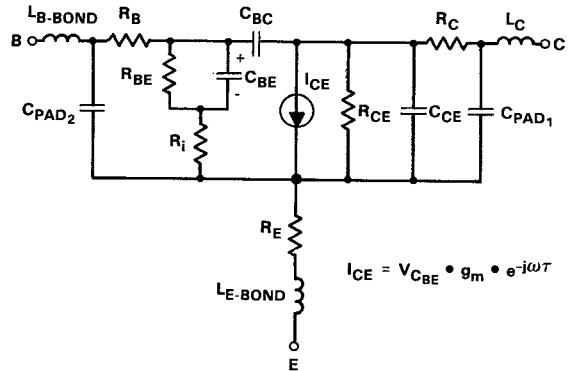

The small-signal equivalent circuit of the device is shown in Figure 4. This circuit was derived from dc measurements and scattering parameter measurements and provided good agreement with our data at frequencies up to 20

|                     |                                            |         |

|---------------------|--------------------------------------------|---------|

| $L_{B\text{-BOND}}$ | BASE BOND WIRE INDUCTANCE                  | 1.0 nH  |

| $L_{E\text{-BOND}}$ | EMITTER BOND WIRE INDUCTANCE               | 1.0 nH  |

| $L_C$               | COLLECTOR CONTACT INDUCTANCE               | 0.01 nH |

| $C_{BE}$            | BASE-EMITTER CAPACITANCE                   | 0.3 pF  |

| $C_{BC}$            | BASE-COLLECTOR CAPACITANCE                 | 0.06 pF |

| $C_{CE}$            | COLLECTOR-EMITTER CAPACITANCE              | 0.03 pF |

| $C_{PAD_1}$         | EMITTER PAD CAPACITANCE                    | 0.05 pF |

| $C_{PAD_2}$         | BASE PAD AND BASE SHORTING BAR CAPACITANCE | 0.08 pF |

| $R_B$               | BASE RESISTANCE                            | 1.5 Ω   |

| $R_C$               | COLLECTOR RESISTANCE                       | 5 Ω     |

| $R_E$               | EMITTER RESISTANCE                         | 2 Ω     |

| $R_{CE}$            | OUTPUT RESISTANCE                          | 170 Ω   |

| $R_i$               | INTRINSIC RESISTANCE                       | 0.8 Ω   |

| $R_{BE}$            | BASE TO EMITTER RESISTANCE                 | 15 kΩ   |

| $g_m$               | TRANSCONDUCTANCE                           | 0.055 S |

Fig. 4 Small-signal equivalent circuit of the Si PBT with top contact as an emitter.

GHz. Both  $f_T$  and  $f_{max}$  are currently limited by device and package parasitics. Analysis of the equivalent circuit shows the intrinsic  $f_{max}$  to be near 40 GHz if chip-carrier parasitics and common-lead bond wire inductances are absent. In addition, the current contact pad areas (base and emitter) are several times larger than the device active region. We anticipate an approximately 20-25% increase in both  $f_T$  and  $f_{max}$  by using 1-mil-diameter pads. Our current devices are also limited by high emitter series resistance which is believed to come from two sources. One source is the high contact resistance between the PtSi emitter and the Al-W bridge; the other source is the relatively small emitter contact surface area resulting from the etched-groove device topology.

#### APPLICATION IN VOLTAGE-CONTROLLED OSCILLATORS

Although GaAs devices are generally superior to Si devices in high frequency performance, they do have one major drawback when used in oscillator applications. They consistently display a rather high level of near-carrier noise, especially phase noise. This noise is due to baseband 1/f noise which is up-converted to the carrier band by the nonlinear mixing mechanisms associated with oscillator operation. The principal source of this noise is generally considered to be depletion layer fluctuations associated with the action of traps in the material. It is well-known that GaAs devices have a higher baseband noise than Si devices.<sup>4</sup> It was for this reason that the Si PBT, which has demonstrated a high frequency capability, was expected to perform well as a low-phase-noise oscillator.

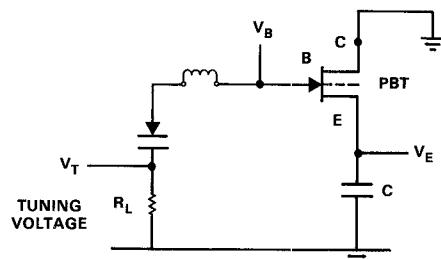

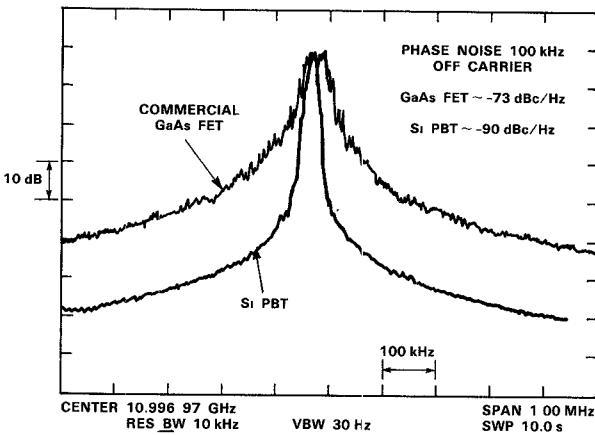

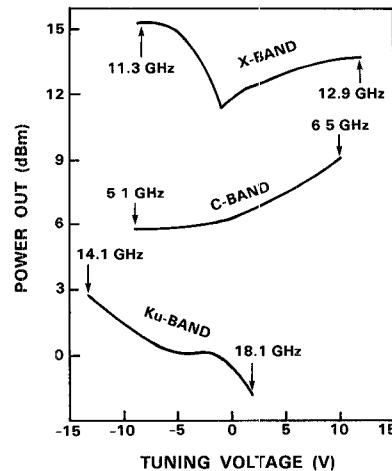

The Si PBT device was placed in a wideband voltage-controlled oscillator (VCO) circuit of the type shown in Figure 5 for all of the oscillator measurements described here. The circuits were optimized for maximum tuning range and not specifically for lowest noise. The device was configured as a two-terminal negative resistance device by inserting a capacitor between emitter and ground with the collector at ground. The resonator circuit is a series L-C network consisting of a varactor tuning diode and an inductor connected between the base terminal and the load,  $R_L$ . The oscillator is tuned by the voltage applied to the varactor diode. Figure 6 compares the oscillator output spectra of a commercial GaAs FET and a Si PBT at a center frequency of 10.996 GHz and a span of 1 MHz. The Si PBT was tested in a circuit that was designed for use with GaAs FETs. The phase noise at 100 kHz away from the carrier frequency is -90 dBc/Hz for the Si PBT and -73 dBc/Hz for the GaAs FET, or approximately 17 dB lower for the Si PBT. Figure 7 shows the output power as a function of tuning voltage for three different Si PBT oscillator circuits built for specific applications at C, X, and Ku bands using identical devices. The circuits were not optimized for high output power alone, but rather for a specific combination of power, phase noise, tuning characteristic, and post-tuning drift settling time. Phase noise that was comparable to the Si PBT VCO of Figure 6 was

Fig. 5 Voltage-controlled oscillator circuit used for all oscillator measurements.

Fig. 6 Comparison of the oscillator output spectrum of a Si PBT with that of a GaAs FET.

Fig. 7 Oscillator output power as a function of tuning voltage for three different Si PBT oscillator circuits. C-band data was obtained at 105°C, while X- and Ku-band data were obtained at room temperature.

observed at all these frequencies under a wide range of bias conditions. We obtained an output power of 33 mW at 11.3 GHz for the small devices (40  $\mu\text{m}$  x 8  $\mu\text{m}$ ) tested here. The output power for the C-band oscillator is lower than that of the X-band oscillator because the C-band circuit contained a linear tuning diode instead of an abrupt junction diode and because the data was taken at a temperature of 105°C.

#### CONCLUSIONS

We have demonstrated voltage-tunable low-phase-noise oscillators at C-, X-, and Ku-band frequencies using Si PBTs. The advantage of the device for oscillator applications arises from the fact that the Si PBT combines the low 1/f and phase noise properties of Si bipolar devices with the high-frequency capability of the GaAs FET. The current device design has not yet been optimized for either low phase noise or high output power, and we believe several improvements can be made in both of these areas with future devices. Because the phase noise properties are affected by material imperfections such as defects and surface states, we believe that the phase noise of the Si PBT could be made even lower by using high quality thermal  $\text{SiO}_2$  on the groove sidewalls and by using epitaxial techniques to produce the desired retrograde doping profiles, which would eliminate the need for ion implantation. In addition, we believe the frequency performance of the Si PBT can be extended to oscillator applications to 50 GHz by reduction of both device parasitics and grating periodicity.

#### ACKNOWLEDGEMENTS

The authors would like to express their appreciation to M.J. McNamara and D.K. Astolfi for device fabrication, to L. Cociani for the small-signal rf measurements, and to B. Fields and E. Grove for the oscillator design and measurements.

The Lincoln Laboratory portion of this work was sponsored by the Department of the Air Force.

#### References

1. C.O. Bozler, G.D. Alley, R.A. Murphy, D.C. Flanders and W.T. Lindley, "Fabrication and Microwave Performance of the Permeable Base Transistor," in IEEE Int. Electron Devices Meet. Tech. Dig., pp. 384-387, Dec. 1979.

2. C.O. Bozler and G.D. Alley, "Fabrication and Numerical Simulation of the Permeable Base Transistor," IEEE Trans. Electron Devices, vol. ED-27, pp. 1128-1141, June 1980.

3. D.D. Rathman, N.P. Economou, D.J. Silversmith, R.W. Mountain and S.M. Cabral, "The Microwave Silicon Permeable Base Transistor," in IEEE Int. Electron Devices Meet. Tech. Dig. pp. 650-653, Dec. 1982.

4. R.A. Pucel, "The GaAs FET Oscillator-Its Signal and Noise Performance," in Proc. of the 40th Annual Freq. Control Symposium, pp. 385-391 (1986).